随着产业的发展,近年来FPGA越来越得到市场的重视,5G、矿机、人工智能、图像识别、risc-v、通信等众多领域均可见到FPGA的身影,目前比较知名的FPGA厂商有xilinx、altera、lattice等,其中xilinx是当之无愧的老大,altera则已于2015年被intel以167亿美元收购,lattice则主要占据一定的中低端份额,国内也有多家FPGA厂商如广东高云、上海安路、西安智多晶、上海遨格芯等,然而目前仍然处于发展初期阶段,和国际厂商在各方面仍然有较大的差距。

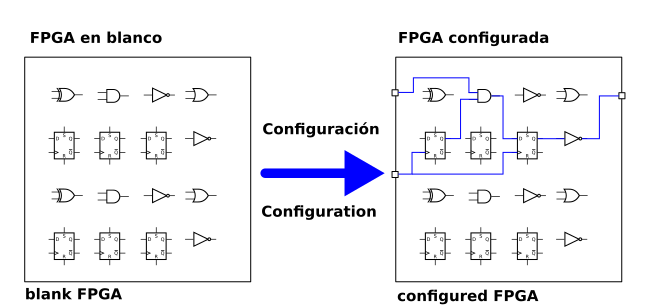

FPGA的基本原理并不算复杂,其内部有一些基本逻辑单元、存储单元、PLL和一些IP,将基本的逻辑单元经过线路的连接,即可组成任意复杂的逻辑,如图所示

FPGA编程即为连线的过程,只不过这些连线并不需要手工连接,而是通过烧录配置文件到FPGA中实现连线(可将配置烧录到外部的Flash芯片或者FPGA内部的RAM中),和软件中的程序概念不太相同,一般将此文件称为配置,或者逻辑。

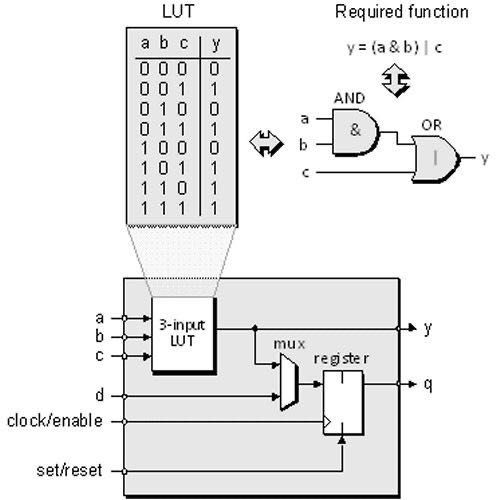

FPGA中的逻辑单元LUT,本质上即为查找表,通过枚举所有的输入输出组合,可以构造出任意的逻辑函数。

由于各个FPGA厂商自己实现了各自的FPGA硬件,功能、性能也不尽相同,所以一般来说厂商都会自己实现配套的EDA软件以供客户开发,例如假若使用xilinx FPGA,需要下载ISE/vivado,若使用altera FPGA则需要下载quartus ii,EDA平台一般提供了一套完整的开发流程,从综合布线到仿真下载以及提供各种IP,当然整套EDA工具都是封闭的,开发者无法了解到底层软件实现的原理,你只需要点击按钮,EDA帮你完成所有操作,然后烧录就可以了。

icestorm是Clifford Wolf 于2015年发起的开源项目,这是主要针对Lattice ICE40系列FPGA芯片的一整套开源的FPGA开发工具链,包含综合(yosys)、布线(arachne-pnr & nextpnr)、时序分析(icetime)、打包(icepack)、烧录(iceprog),这几乎可以说是FPGA发展的一次革命!不需要再下载厂商提供臃肿的IDE和SDK,使用厂商认为你会喜欢的功能,只需使用linux,简单的安装好开源工具链,即可开发FPGA开发,而且,所有东西对你都是透明的,你可以仔细研究任何感兴趣的实现!亦或是直接修改源码做你需要的优化或者研究学习,这在以往的FPGA开发中几乎是不可想象的,开源的魅力就在于此,任何人都可以按照自己的想法自由的修改,这也将让开源工具变得更强大。

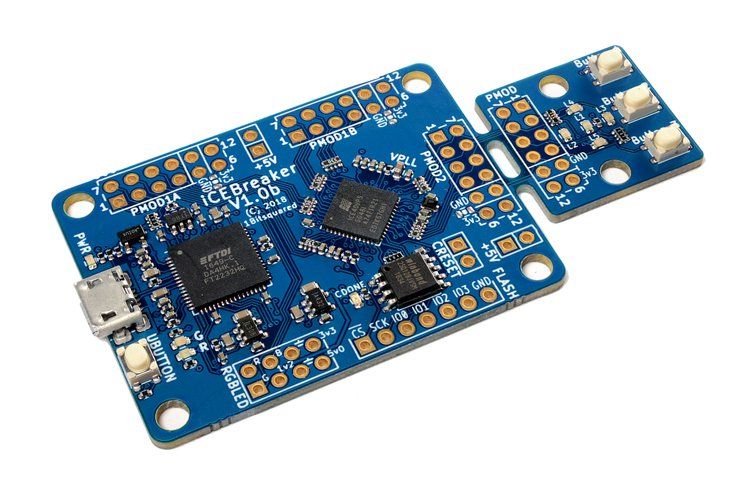

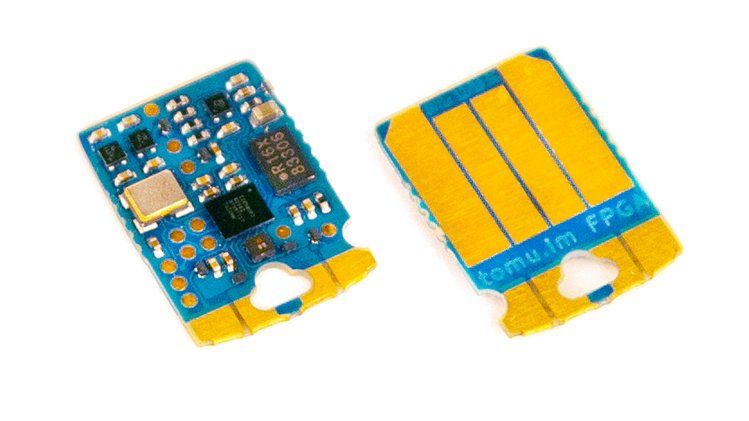

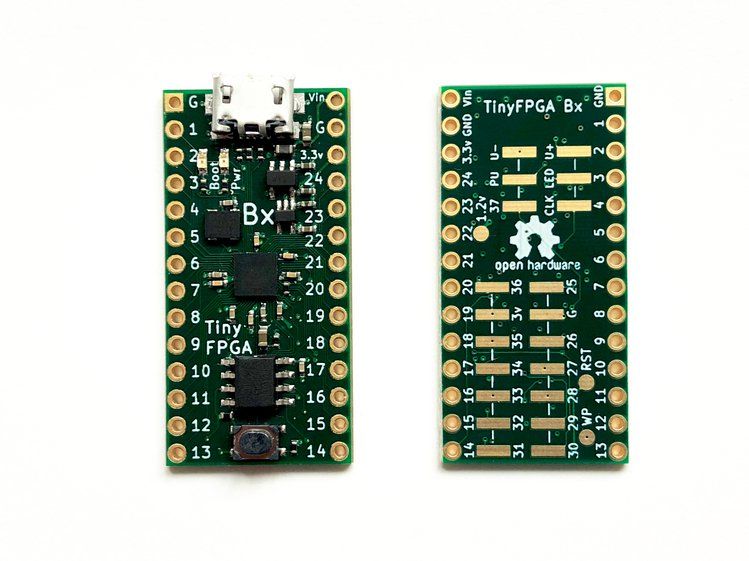

在icestorm开源项目的催生下,国外的创客社区中出现了大量开源开发板,例如成功众筹10W美金,炙手可热的icebreaker,以及将小做到极致的fomu,以及upduino、tinyFPGA、icestick、BlackICE等,均为基于ice40系列的开源单板。

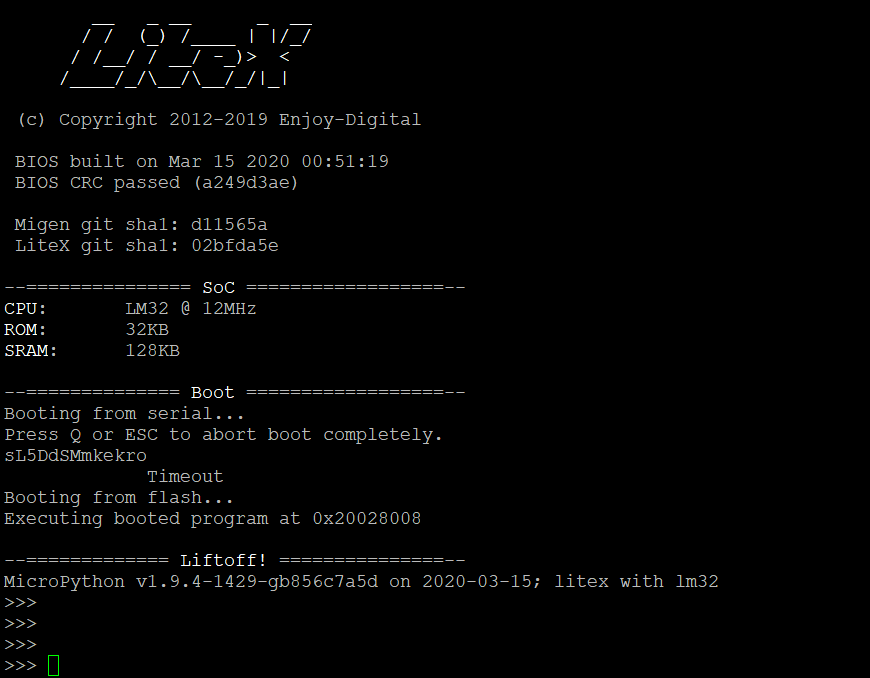

在icestorm和各种开源开发板的推动发展下,也催生出了各种开源FPGA项目,例如基于RISC-V的SoC PicoRV32、iclcle等,强大的SoC框架litex,开源的USB Core ValentyUSB 等,当然,还可以移植各种复古CPU,例如这里是一个完整的6502 PC的实现。

遗憾的是,在国内的FPGA社区中,仍然没有看到基于ICE40,使用icestorm开源工具链的开发板及相关教程,个人认为这套开源的工具链,以及开源的开发模式,对于个人爱好者,或者是资深的开发者,或者是FPGA EDA工具的研究者,都极为有价值。对于个人爱好者来说,社区丰富的demo资料可以用来参考完成各种小项目,资深的开发者也可以进行快速的原型平台验证,EDA工具开发者也可深入挖掘yosys、nexpnr的实现研究原理。

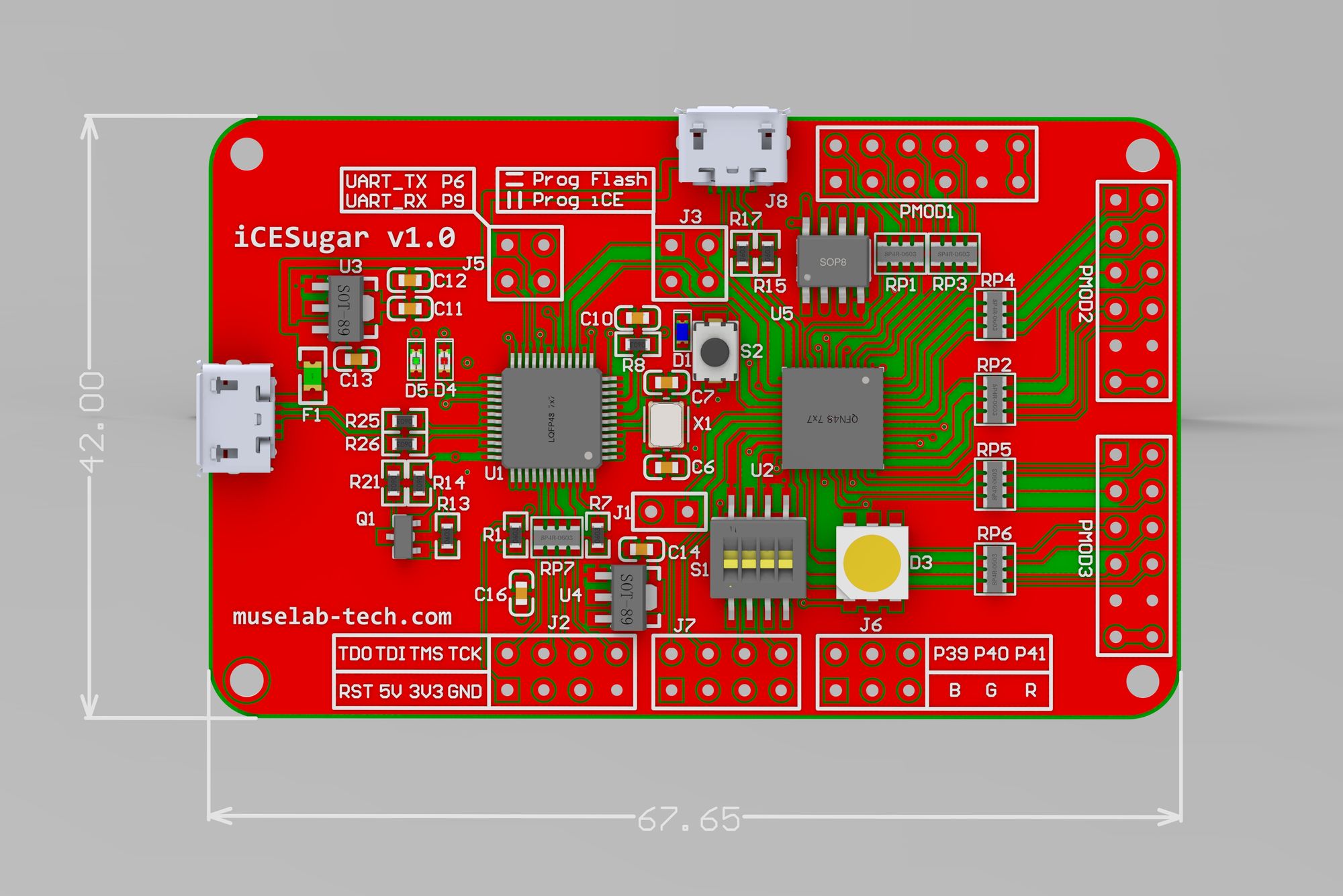

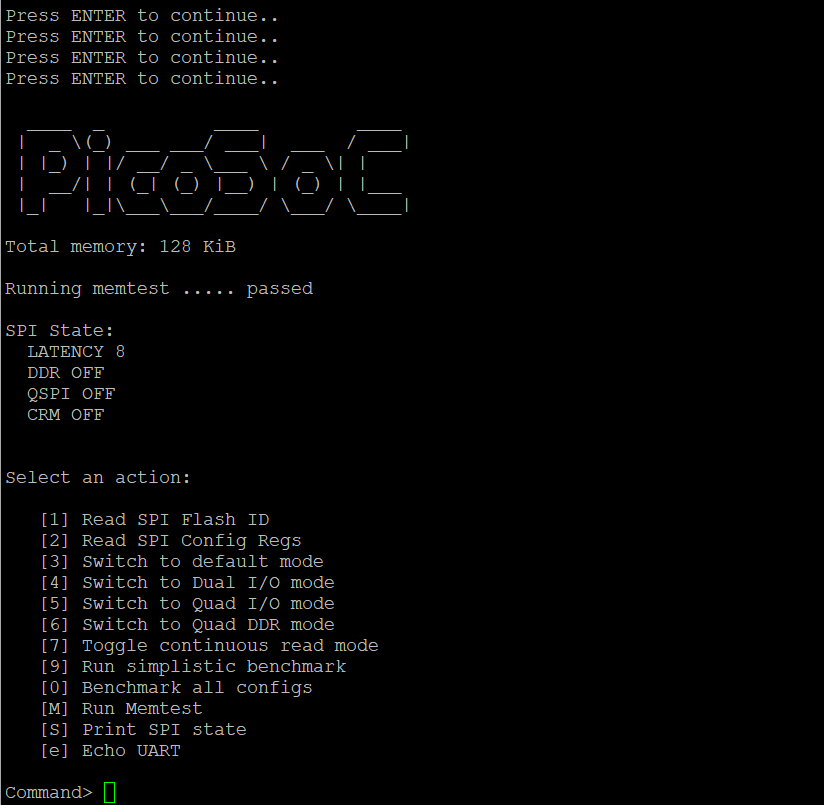

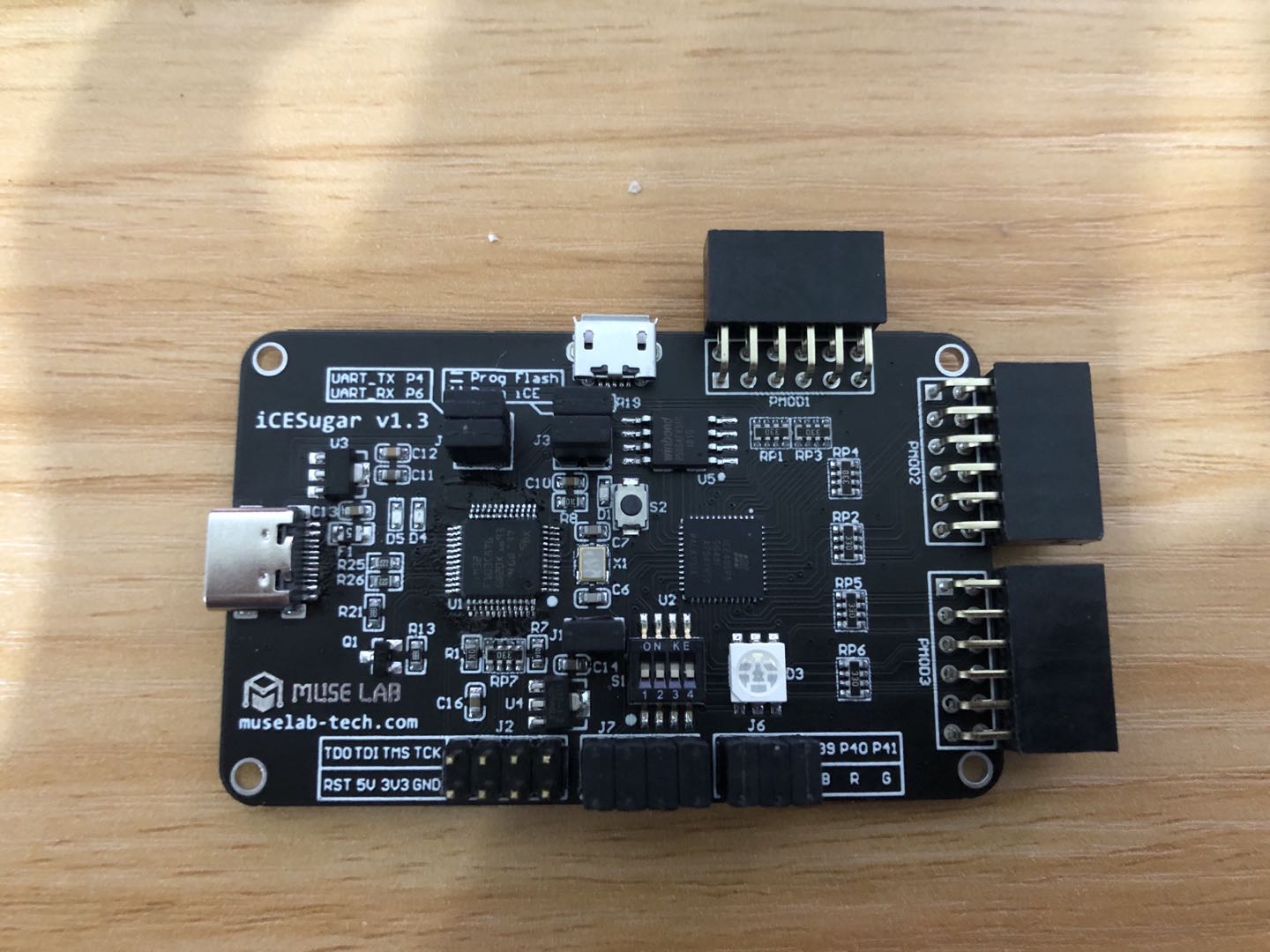

经过一段时间的学习和调研,我自己制作了一块基于iCE40UP5k的开源FPGA单板iCESugar以供研究学习,iCE40UP5k包含5284个LUT,16KB的DPRAM以及128KB的SPRAM,内含PLL、SPI、I2C、DSP、一个外部时钟和两个内部时钟,资源相对较丰富,足够满足日常的学习研究使用。

板子上共有两块主芯片,一片芯片为QFN48封装的iCE40UP5k,另一片则是我基于DAPLink定制实现的烧录系统,芯片使用STM32F1,命名为iCELink,这也是我自认为比较得意的设计,一般开发板中的烧录芯片使用FT2232HL,芯片价格较昂贵,而且只能实现SPI Flash的烧录。而iCELink则充分利用了DAPLink的特性,支持拖拽烧录,只需将FPGA综合出的配置文件拖动到名为iCELink的U盘中,即可实现烧录;同时,iCELink提供CDC 串口,板子上可与FPGA对接进行通信;另外iCELink本身也是基于CMSIS-DAP的开源调试器,支持SWD/JTAG协议,假若FPGA上实现的SoC支持JTAG调试,可将iCELink引出的调试接口直接和FPGA对接,然后在linux使用openocd实现调试(当然你也可以将iCELink当做DAP调试器使用,和其他板子对接进行调试下载);另外,FPGA时钟通过iCELink的PA8引脚的MCO功能输出,一般的单板的时钟方案是FPGA时钟信号直接接到烧录芯片的晶振上,然而这样有一个问题,由于FPGA的引脚是可配置的,一旦不小心将FPGA的时钟信号配置成输出,便会将晶振信号钳位,晶振无法正常起振,烧录芯片无法正常启动,此时单板就挂了,无法再继续烧录,一般的解决方案是在这条时钟线上加上一个跳线帽,使用iCELink的PA8引脚的MCO功能提供时钟则可以完全解决此类问题。

iCESugar的有两个USB接口,一个是iCELink的Type-C接口,用于下载配置,另一个Micro-USB接口直接和FPGA连接,用于将来FPGA上实现USB协议栈的应用,其他大多数接口均已标准PMOD接口引出(这是digilent定义的标准接口),方便将来和多种外设进行对接。

后续还会设计多个PMOD外设以供学习,例如VGA、AUDIO、HDMI、Joystick等,玩法还有很多,敬请期待。

iCESugar项目所有的资料均在https://github.com/wuxx/icesugar ,包含硬件资料原理图、以及当前已经成功适配的系统,另外也有很多基础的demo例子以供爱好者研究学习,同时也真心希望资深的高手能够参与进来一起玩,越多人参与进来形成社区生态,相信会萌发出更多更有意思的项目。另外也欢迎大家加入iCESugar 交流QQ群875160091一起交流学习。

文章的最后,感谢令人尊敬的Clifford Wolf ,Clifford Wolf 先生几乎单枪匹马创造了icestorm的所有组件,没有icestorm项目,就不会有这么多的开源单板和开源项目,我也不可能去做iCESugar开发板。